Хотя я закончил университетский курс по цифровой логике, я новичок в дизайне VHDL, и я надеюсь, что кто-то может помочь мне создать 2 тактовых сигнала, которые зависят от состояния друг друга.Создание двух тактовых импульсов в VHDL

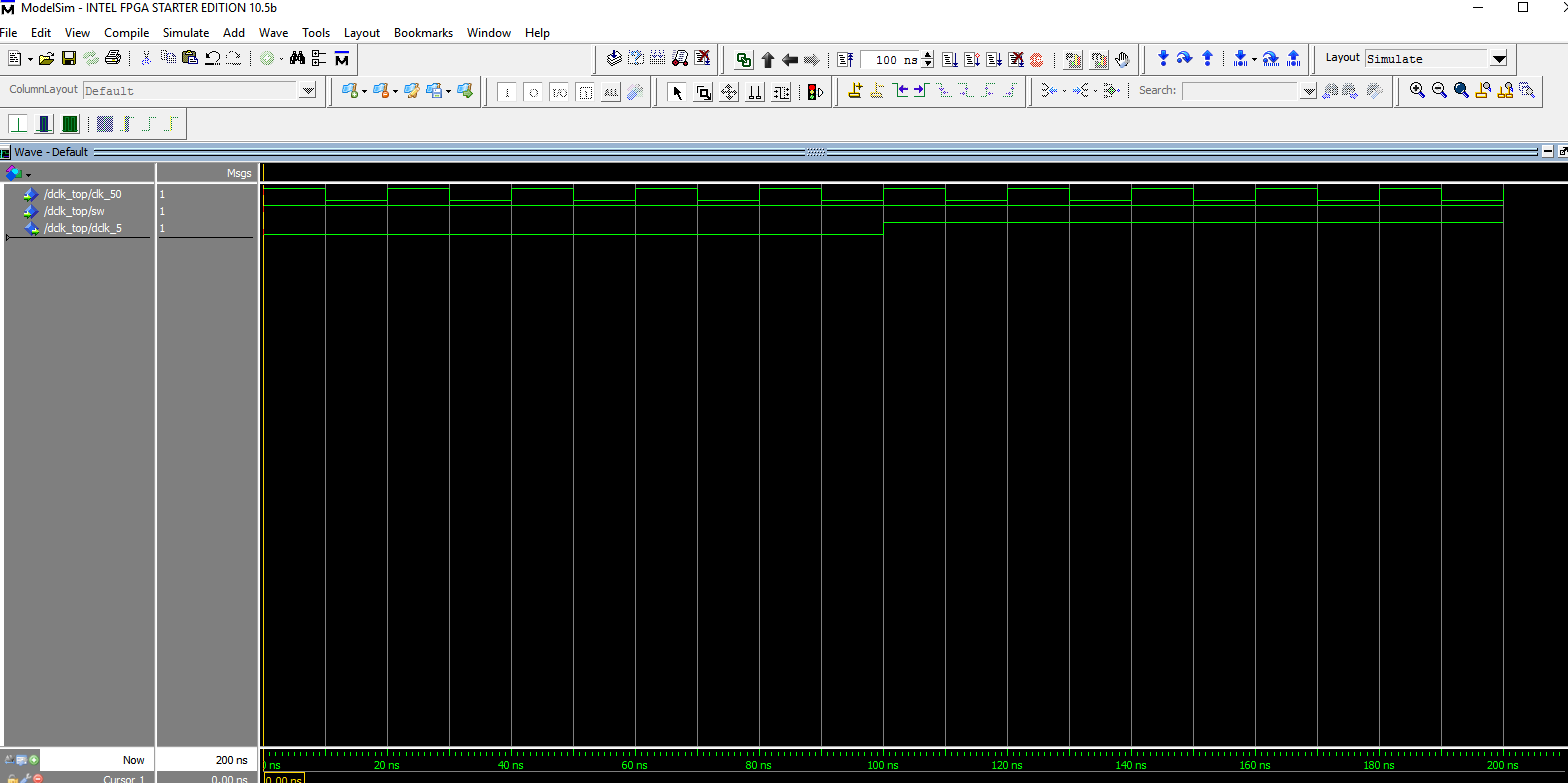

Я использую тактовую частоту 50 МГц на плате FPGA DE2-115, которая используется для создания тактовой частоты 5 МГц (с именем dclk_5). Тем не менее, симуляция показывает два сигнала, но только до 200 нс времени выполнения и больше не будет работать. Почему симуляция не превышает 200 нс?

техническое описание из 2-х часов:

Альтернатива VHDL Дизайн для тестирования dclk_5 и clk_50 который синтезирует, но моделирование не является правильным:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity DCLK_top is

port(

clk_50 : in std_logic;

sw : in std_logic;

dclk_5 : out std_logic

);

end DCLK_top;

architecture behaviour of DCLK_top is

signal clk_counter : integer range 0 to 10 := 0;

signal dclk_counter : integer range 0 to 8 := 0;

signal dclk_pause_counter : integer range 0 to 7 := 0;

signal dclk_pause : std_logic := '0';

signal clk_pause_counter : integer range 0 to 7 := 0;

begin

dclk_proc : process(clk_50)

begin

if(clk_50'event and clk_50='1') then

clk_counter <= clk_counter+1;

if(clk_counter=10) then

clk_counter <= 0;

end if;

if(clk_counter<5) then

dclk_5 <= '0';

else

dclk_5 <= '1';

end if;

end if;

end process dclk_proc;

end architecture behaviour;

Изображение моделирования:

Я не знаю много о Quartus, но нет ли там инструмента для создания таких часов, как xilinx? Вы не объясните, в чем ваша конкретная проблема ... код кажется синтезируемым .... Я бы поставил 'start_dclk = '1'' в другой' if'. – ferdepe

Я использовал ModelSim для генерации часов, но проблема в том, что 50 МГц будет работать нормально в любое время, но когда я включаю dclk (5 МГц), вся симуляция остановится после 400 нс, которая равна 1 циклу dclk. Поэтому я предполагал, что проблема в моем дизайне. Я также обновляю сообщение снимками экрана симуляции. – MrMuffins

Ваш вопрос непонятен, каковы результаты и каковы ожидаемые результаты? См. [Как задать хороший вопрос?] (Https://stackoverflow.com/help/how-to-ask) и [Как создать минимальный, полный и проверенный пример] (https://stackoverflow.com/помощь/mcve). Первоначально он рассматривался как [Quartus VHDL ModelSim, не показывающий, что я хочу] (http://electronics.stackexchange.com/questions/286307/quartus-vhdl-modelsim-not-showing-what-i-want) по обмену стеками электротехники, в разделе «Переполнение стека» разные рекомендации по учетным записям. – user1155120